在图4内,虚线框内是激光发射和接收的光学系统。图中,①、③、⑤为双胶合透镜;②、④为分束镜;⑥为窄带滤波片。这种滤波片的主峰波长为905nm,半宽2nm,主峰偏差0.5nm。

激光发射模块由脉冲驱动电路、激光器、发射光学系统组成;激光接收模块由接收光学系统、光电探测器、信号放大器、整形滤波电路与计数接口电路组成。此外,激光电源由160V高压电源和12V与5V低压电源组成。

激光脉冲测速系统的基本工作原理是,通过双胶合透镜①,将激光器发出的脉冲光聚焦为平行光发射(即激光器的准自系统),然后一部分光经分束镜②、④到光电探测器,这是计时开始时刻t1;大部分光经双胶合透镜③汇聚后射向目标点,经目标点反射回来的散射光先通过笮带滤波片⑥滤除杂波,再由双胶合透镜⑤将微弱的反射光会聚到小面积的光电探测器上,这是计时结束时刻t2。这样,就可得到第1次测量的距离S1=(t2-t1)c/2。同理,对应第2次测量计时开始时刻t3与计时结束时刻t4,可得到测量的距离S2,因而可计算出这段时间内的平均速度

(1)

由于测量时间极短,因此这个平均速度可以认为是瞬时速度(注:任意两次测量开始的时间间隔Δt一样,即驱动电路重复频率的倒数)。

值得提出注意的是,天气是制约激光测速的重要因素,如在大雾天气时激光测速的效果就较差。因为在激光脉冲传播途中存在漫反射,所以为扩大测量范围、提高测量精度,激光脉冲应具有足够的强度。无论怎样改善光束的方向性,总不可避免要有一定的发散,再加上空气对光的吸收和散射,目标越远,反射回来的光能量就越弱,甚至根本接收不到。因此,为了测量较远的距离,一方面要使光源发射具有较高功率密度的光强;另一方面要求激光脉冲的方向性要好。这样,可以把光的能量集中在较小的发散角内,以射得更远一些,光斑更小一些,从而也可准确判断目标的方位。

上述两种措施虽可扩大测量范围,但要提高测量精度,对激光脉冲也还有以下三点要求:

①激光脉冲的单色性要好。因为无论白天还是黑夜,空气中总会存在着各种杀杂散光,它往往会比反射回来的光信号强得多。所以,激光脉冲的单色性越好,窄带滤波片的效果就越佳,就越能够有效提高接收系统的信噪比,保证测量的准确性;

②激光脉冲的宽度要窄。即脉冲上升时间和持续时间要短。因为光速极快,光往返时间极短,光脉冲周期至少应该远远小于光往返时间才能正常测量,并且减小测量误差,还可以提高系统的信噪比;

③接收的探测器的响应速度要足够快。这样,才能有效地提取脉冲信号。

此外,影响激光脉冲测速的范围和精度的因素还有:接收机带宽,计数器计数的精度,天气变化,统计的脉冲误差等。

3、汽车激光测速系统硬件电路的设计

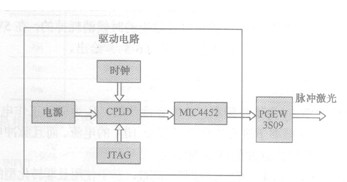

激光脉冲测速系统的硬件电路部分主要由发射模块、接收模块和计算机接口模块3部分组成。激光脉冲测速系统的发射模块硬件结构框架图如图3所示。

图3、激光测速系统的发射模块硬件结构框架图

激光测速系统的发射模块主要由激光管PGEW3S09、驱动芯片MIC4452及CPLD芯片等构成。其工作原理是,从JTAG接口下载程序到CPLD芯片后,CPLD芯片不需要初始化,上电便开始工作,即为由激光管PGEW3S09提供驱动脉冲,同时驱动芯片MIC4452也开始工作。CPLD将在上电后发出极小占空比的测速脉冲,然后将脉冲送给驱动芯片MIC4452。激光管PGEW3S09的输入端连接驱动芯片MIC4452的输出端,由驱动芯片MIC4452产生大电流脉冲驱动,并使激光管PGEW3S09产生脉冲激光输出。

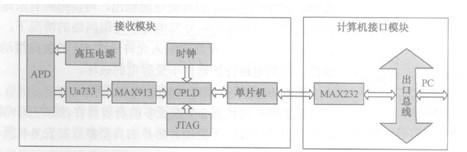

激光测速系统的接收模块和计算机接口模块硬件结构框图如图4所示。

图4、激光测速系统的接收模块和计算机接口模块硬件结构框图

激光测速系统的接收模块和计算机接口模块的基本工作原理是,当激光脉冲经目标物反射回来后,由接收光学系统进行聚焦,集中光能投射至雪崩光电二极管APD。APD将接收到的激光脉冲进行光电转换,变成电信号进入放大器Ua733。而放大器虽放大了信号,但也同时放大了噪声,因而不能提高信噪比。所以,要让信号继续通过比较器MAX913,这样就可设定一阈值,以提取出”干净”的脉冲信号,从而好提高测量精度。经过比较的信号进入CPLD芯片,进行计数和处理,再通过单片机处理,由串口总线送入到PC中进行计算处埋,从而显示输出所测速度值。

4、汽车激光测速系统主要电路芯片选择

(1)激光发射模块主要芯片选择

由前述己知,激光测速系统的发射模块主要由激光管PGEW3S09、驱动芯片MIC4452及CPLD芯片等构成。

①选定的激光二极管为美国EG&G公司生产的PGEW3S09,该管内部是一个容性负载,其典型值是300pF。显然,对一个大的电容负载进行充、放电需要很大的电流。

激光二极管PGEW3S09在10kHz频率下进行工作至少需要10A的电流。并且,脉冲电流的脉冲宽度必须要小于激光管的发射光脉冲的脉宽30ns。

②要有能满足驱动激光二极管PGEW3S09的驱动芯片,现选定MIC4452。该芯片是MICREL公司生产的一款超强、高效,易于使用且非转化型的CMOS MOSFET驱动芯片,它能产生12A的峰值电流输出,可以绰绰有佘地驱动最大MOSFET,在没有任何外部电容和电阻网络的情况下,输入范围在2.4V~Us之间。电路的输入允许最大5V的负向摆动而不破坏器件。附加电路保护器件不受静电的破坏。

由于PGEW3S09的容性负载为300Pf,实际上用MIC4452对应的上升和下降时间为5ns左右,这样脉冲的边沿比较陡,产生的脉冲波形比较好,有利于提高测量精度。

③可编程逻辑器件选用EPM7032S,它是基于Altera公司第2代多阵列矩阵(MAX)绪构,由逻辑阵列块(LAB)、可编程连线阵列(PIA)、I/O控制块等部分组成,并具有高阻抗、电可擦等特点。

设计开发环境采用Altera公司的MAX+Plus Ⅱ软件工具。它是一种集设计输入、编译、仿真、综合、器件编程等功能于一体的完全集成化,易学易用的可编程逻辑设计软件。设计人员无须详细了解器件内部的复杂结构,只需选择自己熟悉的设计输入的方法和工具,即可进行设计输入。该软件提供了一种真正与结构无关的可编程逻辑设计环境,它支持不同结构的器件,如FLEX、MAX、CLASSIC系列器件等。这样,根据算法流程图就可容易地设计出VHDL源文件,然后输入到MAX+Plus Ⅱ软件中进行调试、仿真。通过仿真波形和时序分析等功能可以验证设计的正确性,并能迅速地在不改变硬件电路的情况下修改设计,因而可大大缩短设计周期,提高效率。当确认设计无误后,生成的可配置文件通过Altera公司的编程电缆ByteBlaster装入到可编程逻辑器件EPM7032S中,然后通过调试即可完成整个设计。

(2)发射模块脉冲驱动电路的设计

发射模块脉冲驱动电路是非常重要的,因为脉冲驱动信号,如脉冲的上升与下降时间和脉宽将直接影响输出信号的质量和测量精度。我们选用的CPLD已广泛应用在各种脉冲驱动电路的设计中。CPLD的时钟延迟可达纳秒级,其连续式布线结构也决定了它的时序延迟是均匀的和可预测的。

由于设计要求核心是计数器,即要求准确的确定时间,因此器件内部的时延是必须考虑的而且将准确地预测,并且对时序的要求比较严格,这也是选CPLD的原因。

【中安网原创稿件声明】转载中安网文章时应遵循以下三个规则:1、保持原创文章中图表、图片、音视频的完整性;2、完整标注文章作者[文章前后有说明];3、转载中安网原创中部分内容也要完整标注来源"中安网",违者本网将依法追究。

【想第一时间了解安防行业的重磅新闻吗?请立即关注中安网官方微信(微信号:cpscomcn)——安防行业第一人气微信,万千精彩,千万不要错过!!!

网友评论

共有0条评论 点击查看全部>>24小时阅读排行

本周阅读排行